#### **Asitektur Z80**

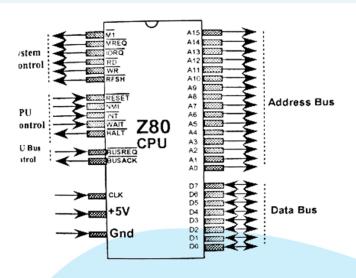

Arsitektur Z80 didesain dengan mengaplikasikan metode standard bus, yaitu pengelompokan jalur-jalur dalam tiga macam bus:

- ✓ Address Bus

- ✓ Data Bus

- √ Control Bus

#### **Asitektur Z80**

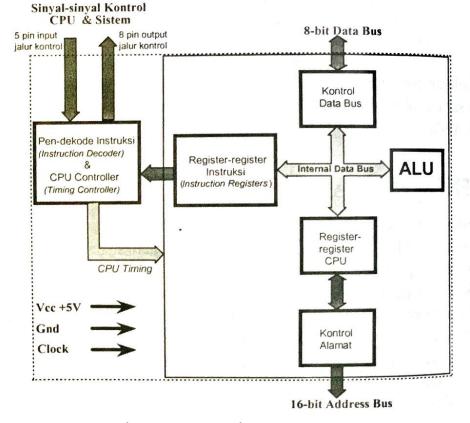

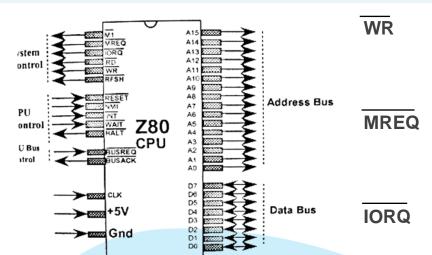

Gambar 9.1 Arsitektur Z80

Gambar 5.1 memperlihatkan arsitektur Z80, baik untuk tipe CMOS maupun tipe *non* CMOS.

CPU Z80 mengaplikasikan metode standar bus (address bus, data bus dan control bus).

Z80 bekerja pada tegangan +5 Volt, memiliki kemampuan kerja 2 MHz, internal register 208 bit, 6 general-pupos regiter yang dapat dipisah (tiap 8 bit), tersedia instruksi exchange yang menunjang fungsi respon interrupt yang cepat.

#### KONFIGURASI PIN BERDASARKAN INPUT/OUTPUT

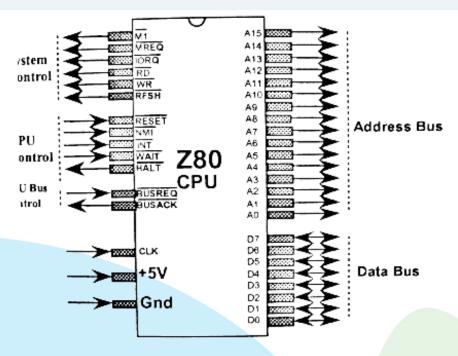

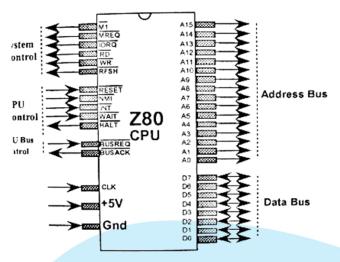

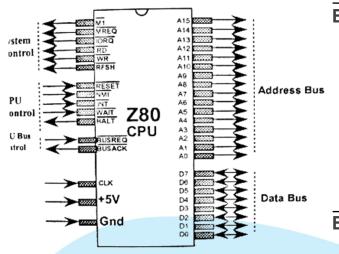

Gambar 9.2 Konfigurasi pin Z80 berdasarkan fungsi Input-Output

#### KONFIGURASI PIN BERDASARKAN INPUT/OUTPUT

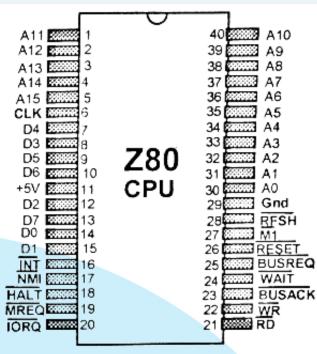

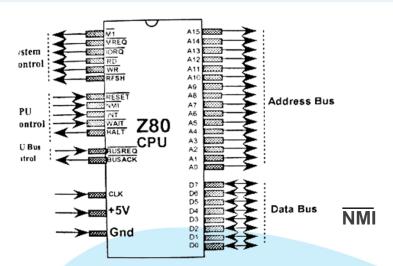

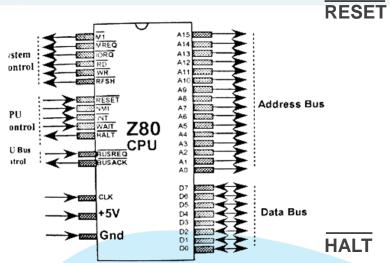

Gambar 9.3 Konfigurasi dalam DIL (Dual In Line Package) 40 pin

CLK

$\overline{RD}$

AO - A15 Address bus, berfungsi sebagai output, dapat memiliki 3 kondisi (high, low dan tri-state). A0 sampai A15 mem bentuk 16-bit address bus dengan posisi A0 sebagai L SB dan A15 sebagai MSB. Kapasitas memori dengan pengalamatan langsung adalah 64KB.

D0 - D7 Data bus, dapat berfungsi sebagai input atau output, bi sa dalam 3 kondisi (low, high dan tri-state). D0 - D7 ad alah 8-bit bidirectional address bus, digunakan untuk p ertukaran data antara CPU dan memori atau rangkaian Input/Output.

Clock, berfungsi sebagai input. Pada jalur ini, harus di berikan pulsa clock dari rangkaian oscillator agar siste m dapat bekerja.

Read, berfungsi sebagai output, active low dan dapat memiliki 3 kondisi (low, high dan tri-state). Adanya siny al aktif menunjukkan bahwa CPU menginginkan suatu proses pembacaan data dari memori atau peralatan In put.

Write, berfungsi sebagai *output*, *active low* dan dapat me miliki 3 kondisi (*low*, *high* dan *tri-state*). menunjukkan bah wa CPU menginginkan suatu proses penulisan data ke memori atau peralatan *Output*.

Memory Request, berfungsi sebagai output, active low, d

apat memiliki 3 kondisi (low, high dan tri-state). Adanya si nyal aktif menunjukkan bahwa address bus sedang berisi alamat yang valid untuk suatu proses read/write memori. Input/Output Request, berfungsi sebagai input/output, act ive low dan dapat memiliki 3 kondisi (low, high dan tri-sta te). Adanya sinyal aktif menunjukkan bahwa A7 - A0 dan address bus sedang berisi alamat I/O yang valid untuk m elakukan operasi *Read* atau *Write* pada peranti I/O terse but. Sinyal juga dihasilkan secara bersamaan dengan sin yal pada saat suatu pemintaan interrupt telah diterima ol eh CPU untuk menunjukkan bahwa instruksi berikut yang merupakan *interrupt vector* boleh ditempatkan di *address* bus.

#### **BUSREQ**

Bus request, berfungsi sebagai input active low. Bila rang kaian luar menginginkan agar suatu saat CPU bus berad a dalam keadaan tri-state dengan maksud akan menggun akan bus tersebut untuk suatu keperluan, maka bus requ est dapat digunakan. Dengan mengaturnya dalam keada an low maka CPU bus. yaitu address bus, data bus, RD, WR, WREQ dan IORQ akan tri-state. Bila telah tri-state, CPU akan memberikan sinyal BUSACK

#### BUSACK

Bus acknowledge, berfungsi sebagai output active low. B us acknowledge berfungsi memberitahu kepada rangkaia n tertentu yang sebelumnya meminta kepada CPU untuk melakukan sesuatu bahwa CPU address bus, CPU address bus dan sinyal-sinyal kontrol RD. WR MREQ dan IORQ telah dalam keadaan high-impedance (tri-state), untuk sel anjutnya rangkaian tertentu tersebut dapat mengontrol bu s-bus untuk digunakan.

**INT**

Interrupt Request, berfungsi sebagai input, active low. Bila peralatan I/O membutuhkan suatu fasilitas agar pada suatu saat dapat melakukan suatu interrupt kepada CPU (interup si terhadap proses yang sedang dikerjakan), maka ia dapat menggunakan kontrol INT ini. Bila INT diaktifkan maka CP U akan melakukan interupsi terhadap program yang sedan g dijalankan dan akan menuju ke suatu program yang telah didefinisikan sesuai dengan pemberian instruksi INT . Alam at awal program rutin Interrupt ini disebut sebagai Interrupt Vector.

Non-Maskable Interrupt. berfungsi sebagai input, negative edge-triggered. NMI memiliki prioritas yang lebih tinggi dari pada INT. Maksudnya bila pertama diberikan INT kemudian NMI, maka CPU akan memperhatikan NMI meskipun prose s yang dikehendaki oleh INT belum selesai. Namun, bila diberikan NMI terlebih dahulu dan kemudian INT, maka INT ha rus menunggu proses yang dikehendaki NMI selesai terlebih dahulu baru INT akan diperhatikan. Pada setiap pemberian sinyal NMI, CPU akan melakukan proses jump ke alamat 0066H.

Reset, berfungsi sebagai input, active low. Mengaktifkan RES ET berarti menginisialisasi CPU kembali ke posisi: PC diset 0 000H, semua register termasuk I dan R di-clear-kan dan inter rupt status diset dalam mode 0. Selama reset terjadi, address bus dan data bus berada dalam kondisi high-impedance (tri-s tate), sedang semua sinyal kontrol output berada dalam kead aan tidak aktif (inactive). Untuk mendapatkan hasil reset yang lengkap, sinyal RESET harus diberikan minimal selama 3 sik lus clock secara penuh.

Halt State, berfungsi sebagai output, active low. Sinyal HALT yang muncul menunjukkan bahwa CPU telah mendapat perin tah HALT dari program untuk menghentikan proses kerjanya sementara, sampai ia mendapat sinyal interrupt, baik NMI ma upun INT. Selama menunggu sinyal interrupt, CPU menjalan kan instruksi NOP (no operation) secara berulang untuk menjaga agar memori (dynamic RAM, jika memakai) tetap valid.

MI

Machine Cycle One, berfungsi sebagai output, active low. bersama sama dengan RFSH menunjukkan bahwa siklus mesin (operasi) yang sedang berjalan pada saat itu adal ah opCode fetch cycle (siklus pengambilan Opcode) dari eksekusi sebuah instuksi.

**RFSH**

Refresh, berfungsi sebagai *output*, *active low*. RFSH dan bersama sama menunjukkan bahwa konfigurasi A7—A0 pada *address bus* dapat digunakan sebagai *refresh address* ke sistem memori dinamik.

WAIT

Wait, berfungsi sebagai input, active low. Bila aktif berarti CPU sedang diberitahu bahwa memori atau peralatan I/O yang dialamati oleh CPU belum siap memberikan datany a untuk ditransfer. Bila ini muncul, CPU akan menunda pekerjaannya, menunggu sampai kontrol tidak aktif...

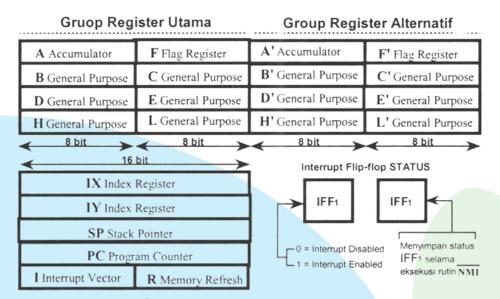

CPU Z80 memiliki Read/Write memori yang disebut register sebanyak 280 bit, atau 26 x 8 bit. Memori di dalam CPU ini sangat berguna bagi programmer da lam pembuatan program. Internal memori ini dibagi dalam 18 buah register 8 -bit dan 4 buah register 16 bit, seperti ditunjukan pada Gambar 5.4.

Gambar 9.4 Register-register CPU Z80

# Pewaktuan Read/Write Memori Mikroprosessor Z80

PERTEMUAN / MATERI KE 10

Antarmuka dan Kamputer

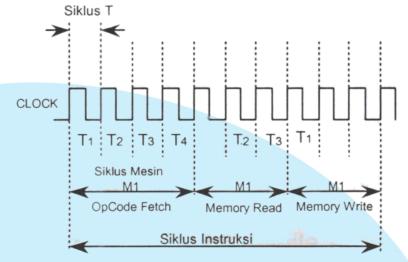

## SISTEM TIMING CPU Z80

Seperti ditunjukan pada Gambar 10.1., sebuah periode *clock* dinyatakan sebag ai siklus T, sedangkan operasi dasar dinyatakan sebagai M (*Machine Cycle*). *M achine cycle* atau siklus mesin terdiri dari M1, M2 dan M3. M1 memiliki 4 bua h siklus T, yaitu T1, T2, T3 dan T4. M2 memiliki 3 buah siklus T, yaitu T1, T2 dan T3. Demikian pula M3 memerlukan waktu 3 siklus T, yaitu T1, T2 dan T3.

Gambar 10.1 Timing dasar operasi pada CPU Z80

Dalam operasi program, siklus mesin ya ng pertama (M1) dari setiap instruksi a dalah *fetch cycle* (pengarnbilan OpCode untuk di-dekode. Siklus ini membutuhk an 4 sampai 6 siklus, terkecuali bila kon trol WAIT diaktifkan, siklus dapat diperpanjang.

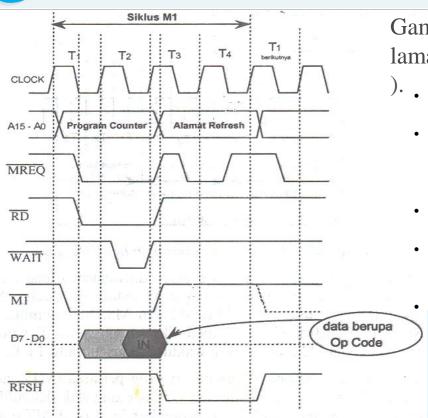

#### PEWAKTUAN OPCODE FETCH

Gambar 10.2 menunjukkan diagram pewaktuan se lama siklus mesin MI (Operation Code fetch cycle

- Pertama, siklus MI address bus berisi data yang tersimpan di Progra m Counter (PC).

- Setengah *clock cycle* berikutnya, sinyal MREQ menjadi aktif. Pada s aat ini, langsung sebagai kontrol chip *enable* pada memori. Kontrol RD juga menjadi aktif yang digunakan untuk proses pembacaan data memori. CPU mengambil data dari memori

- Pada saat *rising edge* T3 dan pada waktu yang bersamaan pula CPU meng-inactivekan sinyal MREQ dan RD.

- Clock state T3 dan T4 digunakan untuk merefresh dynamic memory.

Pada State ini, Å7—A0 dari address bus berisi alamat memori yang di-refresh dan sinyal kontrol RFSH menjadi åktif.

- Sinyal RD tidak aktif selama T3 dan T4 menjaga agar data dari segm en memori yang berbeda tidak terhubung ke *address bus*. Selama *refr esh*, sinyal MREQ juga aktif dengan selang waktu yang lebih pendek dan berada di tengah-tengah Waktu aktif dari sinyal MREQ ini biasa nya juga di gunakan bersama-sama dengan RFSH.

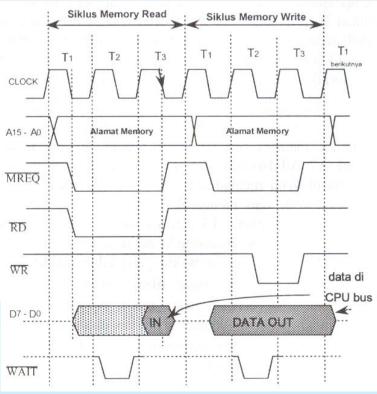

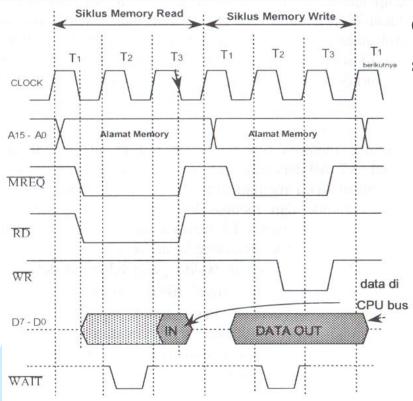

#### **PEWAKTUAN MEMBACA MEMORI**

Gambar 10.3 Pewaktuan siklus OpCode fetch

Gambar 10.3 menunjukkan diagram pewaktuan dari siklus Read pada CPU Z80. Pada umumnya terdiri dari 3 buah si klus T, Kecuali WAIT diaktifkan.

- Saat *Write cycle* T1, T2, T3 alamat memori yang akan di tulis, mulai dilet akkan di *address bus*. Begitu rising edge T1 terjadi, alamat memori yang akan dituju diletakkan di *address bus*.

- Begitu T1 mengalami rising edge, MREQ dan RD bersama-sama aktif be gitu T1 menuju ke 0 pada Sisi *falling edge. Wait state* dapat ditambahkan dengan mengaktifkan WAIT pada *falling edge* pulsa clock berikutnya, da lam hal ini adalah T2.

- Data yang akan dibaca berada di address bus pada saat siklus berada di T

3. Data ini diambil oleh CPU berdasarkan falling edge dari T3. Berdasark

an *falling edge* ini pula, sesaat kemudian MREQ dan RD menjadi *inactive*kembali.

#### PEWAKTUAN MENULIS MEMORI

Gambar 10.4 Pewaktuan siklus OpCode fetch

Gambar 10.4 menunjukkan diagram pewaktuan dari siklu s Write pada CPU Z80.

- Pada *Write cycle* memiliki T1, T2 dan T3. Alamat memori yang akan di tulis mulai diletakkan di address bus begitu *rising edge* T1 terjadi.

- Berdasarkan falling edge T1 MREQ menjadi aktif. Begitu MREQ aktif, data bus akan diisi data oleh CPU. Data ini adalah data yang akan dituli skan oleh CPU ke memori.

- Wait state dapat ditambahkan dengan mengaktifkan pada saat *rising ed ge* T2 telah stabil. Sinyal aktif begitu *falling edge* T2 terjadi. Pada saat inilah rangkaian memori mengambil data yang telah ada di *address bus*. Berikumya, berdasarkan *falling edge* T3, sinyal MREQ dan WR menjadi *inactive* kembali.

# PEWAKTUAN INPUT/OUTPUT dan READ/WRITE MIKROPROSESSOR Z80

PERTEMUAN / MATERI KE 11

Antarmuka dan Kamputer

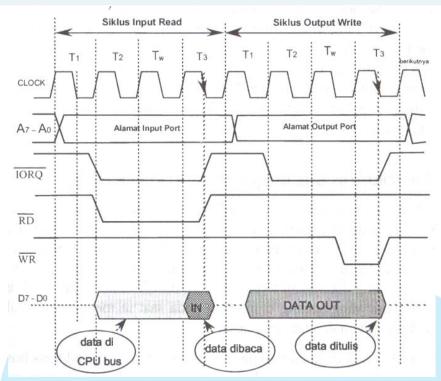

# PEWAKTUAN INPUT/OUTPUT READ/WRITE

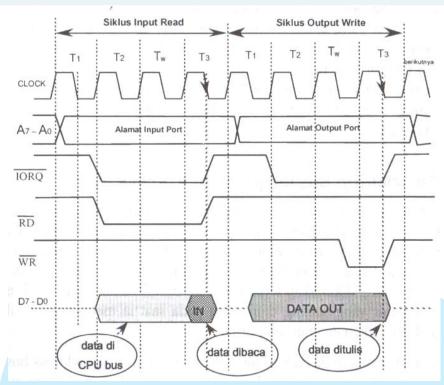

Pada operasi Input read maupun *output write*, secara otomatis sebuah *wait state* (Tw) ditambahkan setelah T2.

#### Alasannya adalah:

Waktu yang tersedia dari sinyal  $\overline{IORQ}$ ,  $\overline{RD}$  atau  $\overline{WR}$  (aktifnya sinyal  $\overline{IORQ}$  sampai *falling edge* T3) untuk menjadi inactive kembali, tidak cukup untuk membuat data yang ditransfer melalui *address bus* menjadi se mpurna atau siap untuk ditransfer.

#### PEWAKTUAN MEMBACA MASUKAN

Gambar 11.1 Pewaktuan siklus OpCode fetch

# Gambar 11.1 Menunjukkan pewaktuan dari operas i *Input Read* dan *Output Write*

- Pada Tl, begitu rising edge terjadi, address bus diisi dengan alam at port (terminal) yang dituju untuk dibaca datanya. Tl hanya dig unakan untuk mengaktifkan address bus.

- Berdasarkan rising edge T2, sinyal IORQ dan RD bersama-sama menjadi aktif untuk mengaktifkan kontrol-kontrol peripheral I/O, misalnya semacam (Chip Select).

- Data yang akan dibaca oleh CPU diletakkan di data bus pada saat rising edge T2, berdasarkan falling edge T3, data tersebut diambi

l oleh CPU.

- Sesaat kemudian, sinyal IORQ dan RD menjadi inactive kembali.

#### PEWAKTUAN PENULISAN PADA UNIT KELUARAN

Gambar 11.2 Pewaktuan siklus OpCode fetch

Gambar 11.2 menunjukkan pewaktuan dari operasi *I* nput Read dan Output Write (lajutan)

- Proses Output write dimulai dengan diisinya address bus dengan alamat Output Port yang akan dituju, untuk diisi dengan suatu da ta begitu rising edge Tl terjadi.

- Setelah Tl mengalami *falling edge*, CPU mengisi data bus denga n data yang akan dituliskan.

- Berdasarkan *rising edge* T2, sinyal  $\overline{\text{IORQ}}$  menjadi aktif. Sesaat k emudian, sinyal  $\overline{\text{WR}}$  juga menjadi aktif. pada saat inilah *Output Port* mulai mengambil data yang telah tersedia di *address bus*.

- Proses penulisan data ini berakhir begitu T3 mengalami *falling e dge*. Begitu *falling edge* T3 terjadi, sinyal IORQ dan WR bersam a-sama menjadi *inactive* kembali.

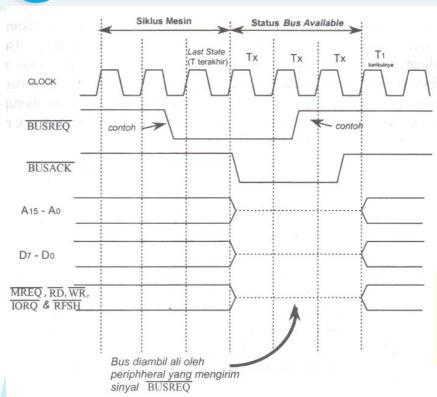

#### PEWAKTUAN BUS REQUEST/ACKNOWLEDGE

Bila Z80 sedang berada dalam suatu proses kemudian diaktifkan maka Z80 akan mela ksanakan permintaan untuk membuat CPU bus menjadi *high impedance* atau *tri-state* setelah *rising edge* siklus T terakhir dari proses siklus mesin yang sedang dikerjakan t erjadi. Hal ini dimaksudkan agar eksekusi instruksi terakhir yang sedang dijalankan p ada saat ia menerima sinyal aktif BUSREQ diselesaikan dengan sempurna.

#### PEWAKTUAN BUS REQUEST/ACKNOWLEDGE

Gambar 11.3 memperlihatkan pewaktuan dari siklus *b us request/Aclmowledge*.

Setelah rising edge dafi siklus T berikut terjadi maka address bus, data bus dan control bus yang terdiri dari kontrol-kontrol bersama-sama menjadi tri-state. Sebagai tanda dari CPU ke p eripheral yang meminta (meminjam) bus (sinyal BUSACK menjadi aktif). Pada Saat ini, bus dapat dipakai oleh rangkaia n luar untuk proses kerja yang dikehendaki.

Umumya, fasilitas seperti ini dimanfaatkan oleh rangkaian luar untuk me lakukan proses transfer data secara langsung antar-peripheral tanpa mem inta pertolongan CPU.

Gambar 11.3 Pewaktuan siklus BUSREQ (*Bus Reques*) dan BUSACK (*Bus Acknowledge*)

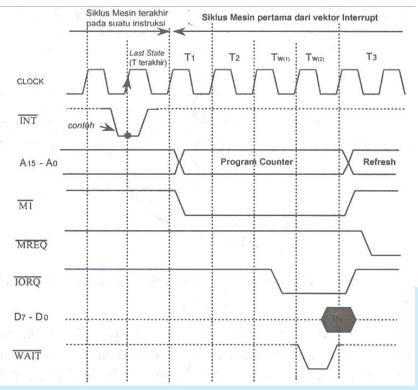

# PEWAKTUAN SIKLUS INTERRUPT REQUEST/ACKNOWLEDGE

Seperti pada pengaktifkan sinyal BUSREQ, permintaan akan di laksanakan oleh CPU, setelah siklus T dari siklus mesin yang se dang dijalankan berakhir.

#### PEWAKTUAN SIKLUS INTERRUPT REQUEST/ ACKNOWLEDGE

Gambar 11.4 memperlihatkan pewaktuan bila sinyal kontrol INT diaktifkan.

- Diperlihatkan bahwa INT diberikan pada saat siklus mesi n berada di permulaan siklus T yang terakhir, dengan de mikian CPU menyelesaikan terlebih dahulu proses siklus mesin tersebut.

- Begitu berakhir (*rising edge* T1), maka CPU akan mengisi address bus dengan suatu program counter yang merup akan vektor alamat.

Gambar 11.4 Pewaktuan siklus Interrupt (INT)

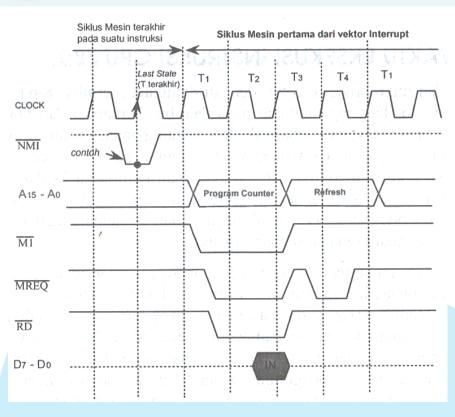

Sinyal kontrol NMI ini memunyai prioritas yang lebih tinggi da ri pada sinyal kontrol, tetapi masih lebih rendah satu tingkat dari sinyal kontrol RESET.

#### Catatan:

- Permintaan NMI akan dilaksanakan terlebih dahulu sampai tuntas, baru kemudian NT.

- Suatu contoh jika INT diberikan terlebih dahulu, kemudian diikuti pemberian NMI, maka meskipun CPU belum menyelesaikan tugas yang diminta oleh INT. CPU akan menunda pe kerjaannya dan melaksanakan tugas yang diminta oleh NMI

#### PEWAKTUAN SIKLUS NON MASKABLE INTERRUPT (NMI)

Gambar 11.5 memperlihatkan pewaktuan dari proses  $request/aclmowledge\ cycle$ , untuk sinyal interrupt ya ng berasal dari  $\overline{\text{NMI}}$ .

- NMI diberikan pada saat yang sama seperti contoh pada pemberian sinyal.

- Satu siklus T berikutnya, CPU baru melaksanakan permintaan NMI dengan mengisi address bus dengan alamat 0066H, atau PC diset 00 66H. Bersamaan itu pula, sinyal NMI menjadi aktif.

- Begitu Tl mengalami falling edge maka sinyal MREQ dan RD menj adi aktif. Pada saat inilah data yang berada di alamat memori yang dihubungi dengan alamat 0066H, diambil oleh CPU untuk didekode dan dieksekusi.

- Selama T3 dan T4, CPU mengaktifkan MREQ dan RFSH, untuk me lakukan memori *refresh*.

Gambar 11.5 Pewaktuan siklus Non-Maskable Interrupt (NMI)